Introducción

El muestreo de las señales en tiempo continuo reemplaza la señal en tiempo continuo por una secuencia de valores en puntos discretos de tiempo. El proceso de muestreo se emplea siempre que un sistema de control involucra un controlador digital, ya que son necesarias para llevar a cabo el muestreo y una cuantificación para ingresar datos a ese controlador. También se da el proceso de muestreo cuando las mediciones necesarias para control se obtienen en forma intermitente.

El proceso de muestreo es seguido por el proceso de cuantificación, la cual, la amplitud analógica muestreada se reemplaza por una amplitud digital (mediante números binarios). La salida de la computadora es una señal muestreada que se alimenta a un circuito de retención. La salida del circuito de retención es una señal en tiempo continuo que se alimenta al actuador. Para el este concepto, al hablar de discretización, se habla del análisis de sistemas con entradas y salidas múltiples.

Circuitos de muestreo y retención.

Un muestreador convierte la señal analógica en un tren de pulsos de amplitud modulada dentro de un sistema digital. El circuito de retención mantiene el valor del pulso de la señal muestreada durante un tiempo específico. El muestreador y el retenedor son necesarios para el convertidor A/D (analógico a digital) para producir un número que represente la señal de entrada en el instante de muestreo. Existen circuitos de muestreo y retención de una sola unidad, conocidos como muestreador y retenedor (S/H). Sin embargo, matemáticamente, las operaciones de muestreo y la de retención se modelan por separado. Es una práctica común utilizar un convertidor de analógico-digital y multiplexar varias entradas analógicas muestreadas en éste.

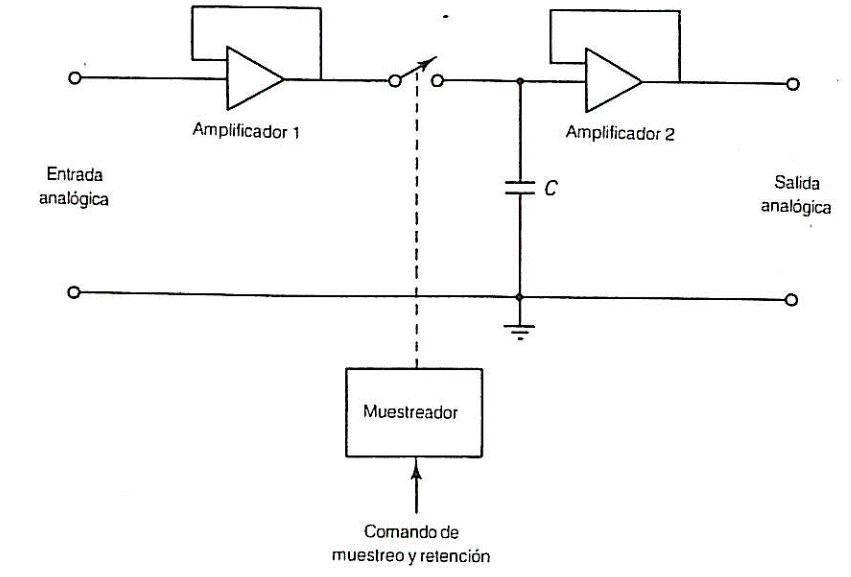

En la figura 1 se muestra un diagrama simplificado para el muestreador y retenedor. Este circuito es analógico (simplemente un dispositivo de memoria de voltaje) en el que se adquiere una entrada de voltaje y entonces se almacena en un capacitor con características de fuga y absorción dieléctrica bajas.

En este circuito el interruptor electrónico se conecta la capacitor de retención. El amplicador 1 es un amplificador de aislamiento de entrada con una impedancia de entrada alta. El amplificador 2 es el amplificador de salida; éste aísla el voltaje en el capacitor de retención.

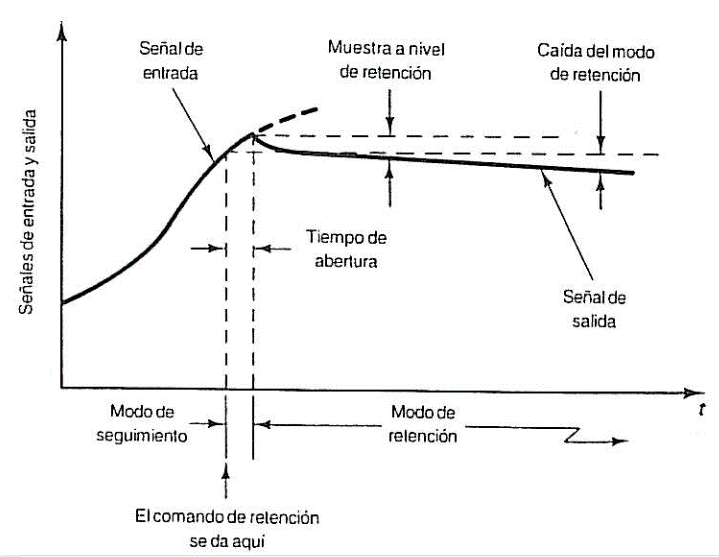

Existen dos modos de operación para el circuito de muestre y retención: el modo seguimiento y el de retención. Cuando el interruptor está cerrado (esto es, cuando la señal de entrada está conectada), el modo de operación es el seguimiento. La carga en el capacitor en el circuito sigue al voltaje de entrada. Si el interruptor está abierto (señal de entrada desconectada), el modo de operación es el de retención y el voltaje del capacitor se mantiene constante por un tiempo específico (figura 2).

En la práctica, la conmutación en modo seguimiento al de retención no es instantáneo. Si se da el comando de retención mientras el circuito está en el modo de seguimiento, entonces el circuito permanecerá en el modo de seguimiento por un momento antes de reaccionar ante el comando de retención. El intervalo de tiempo durante el cual la conmutación tiene lugar (esto es, el intervalo de tiempo cuando la amplitud medida es incierta) se denomina tiempo de abertura.

El voltaje de salida durante el modo de retención puede decrecer ligeramente. La caída del modo de retención se puede reducir mediante el uso de un amplificador de aislamiento de salida con una impedancia de entrada alta. Dicho amplificador de aislamiento de salida debe tener una corriente de polarización muy baja. La operación de muestreo y retención está controlada por un reloj.

Reconstrucción de la señal de entrada mediante circuitos de retención

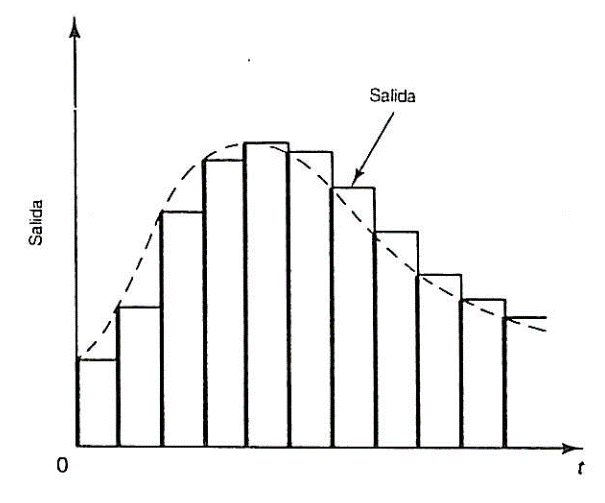

La operación de muestreo produce una señal de pulsos modulados en amplitud. La función de la operación de retención es reconstruir la señal analógica que ha sido transmitida como un tren de pulsos muestreados. El propósito de la operación de retención es rellenar los espacio entre los períodos de muestreo y así reconstruir en forma aproximada la señal analógica de entrada original.

El circuito de retención se diseña para explotar la señal de salida entre pulsos sucesivos de acuerdo con alguna manera preestablecida. La forma de onda de escalera de la salida es la más sencilla para reconstruir una señal de entrada original. Este circuito se conoce como retenedor de orden cero y este se emplea en sistemas de control digital.

Se dispone de circuitos de retención más sofisticados que el de orden cero. Estos se conocen como circuitos de retención de orden superior e incluyen los retenedores de primer y segundo orden. En general, los circuitos de retención de orden superior reconstruirán una señal de manera más exacta que los retenedores de orden cero, pero con algunas desventajas.

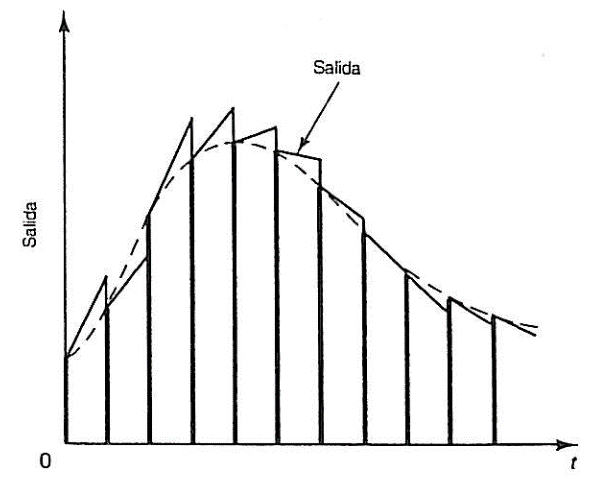

El retenedor de primer orden mantiene el valor de la muestra anterior, así como la del presente, y mediante una extrapolación predice el valor de la muestra siguiente. Esto se logra mediante la generación de la pendiente de salida igual a la pendiente de un segmento de línea que se conecta la muestra actual con la anterior y proyectando ésta desde el valor de la muestra actual.

En la figura 4, si la pendiente de la señal original no cambia mucho, la predicción es buena. En cambio, si la señal original invierte su pendiente, la predicción es mala y la salida sigue la dirección equivocada, provocando un gran error para el periodo de muestreo considerado.

Un retenedor de primer orden con interpolación (llamado retenedor poligonal), reconstruye la señal original mucho más exacta. Este circuito también genera una línea recta a la salida cuya pendiente es igual a aquella que une el valor de la muestra anterior con el valor de muestra actual, pero esta vez la proyección se hace desde el punto de la muestra actual con la amplitud de la muestra anterior. Por lo tanto, la exactitud al reconstruir la señal original es mejor que para otros circuitos de retención, pero existe un período de muestreo de retardo. En efecto, la mejoría en la exactitud se logra a expensas de un retardo de un período de muestreo. Desde el punto de vista de la estabilidad de los sistemas de lazo cerrado, dicho retardo no es deseable, y de este modo el retenedor de primer orden con interpolación (retención poligonal) no se emplea en aplicaciones de sistemas de control.

no tienes ni fookin idea man

Me gustaMe gusta