Circuitos para la retención de datos

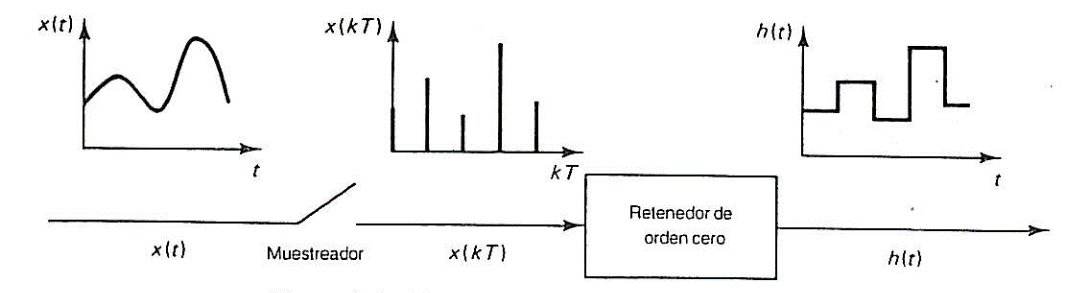

En un muestreador convencional, un interruptor se cierra cada período demuestreo para admitir una señal de entrada. En la práctica, la duración del muestreo es muy corta en comparación con la constante de tiempo más significativa de la planta. Se debe recordar que un muestreador convierte una señal en tiempo continuo en un tren de pulsos que se presenta en los instantes de muestreo

donde

es el período de muestreo. También, si entre dos instantes de muestreo consecutivos el muestreador no transfiere información; dos señales cuyos respectivos valores en los instantes de muestreo son iguales darán como resultado la misma señal muestreada.

La retención de datos es un proceso de generación de una señal en tiempo continuo a partir de una secuencia en tiempo discreto

. Un circuito de retención convierte la señal muestreada en una señal en tiempo continuo, que reproduce aproximadamente la señal aplicada al muestreador. La señal

durante el intervalo de tiempo

se puede aproximar mediante un polinomio en

como sigue:

donde . Si la señal

debe ser igual a

, la ecuación anterior se puede escribir como

Si el circuito de retención de datos es un extrapolador polinomial de n-ésimo orden, se conoce como retenedor de n-ésimo orden. El retenedor de n-ésimo orden emplea datos discretos anteriores

,

, … ,

para generar una señal

.

Debido a que un retenedor de alto orden utiliza muestras anteriores para extrapolar una señal en tiempo continuo en el instante de muestreo presente y el siguiente, la exactitud en la aproximación de la señal en tiempo continuo se mejora a medida que el número de muestras anteriores utilizadas se incrementa. Sin embargo, esta mejoría se obtiene a costa de un tiempo de retraso mayor. En sistemas de control de lazo cerrado, cualquier tiempo de retardo adicional en el lazo hará una inestabilidad del sistema.

Retenedor de orden cero

El retenedor más sencillo se obtiene cuando , esto es, cuando

donde y

. Esta ecuación implica que el circuito retiene la amplitud de la muestra de un instante muestreo al siguiente. Dicho retenedor de datos se conoce como retenedor de orden cero, o sujetador, o generador de la señal de escalera. La salida del retenedor de orden cero es una función escalonada.

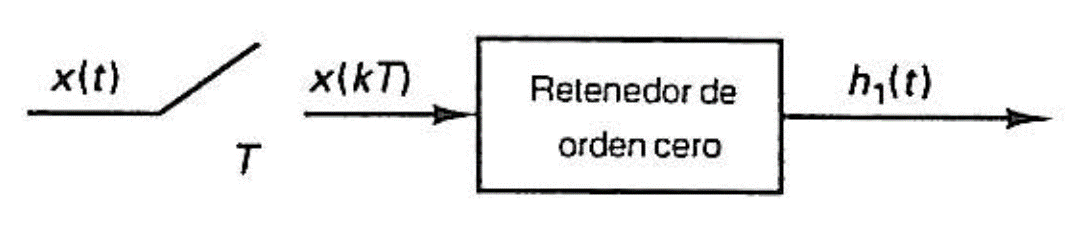

La señal de entrada se muestrea en instantes discretos y la señal muestreada se pasa a través del retenedor de orden cero. El circuito retenedor de orden cero suaviza la señal muestreada para producir la señal

, la cual es constante desde el último valor muestreado hasta que se pueda disponer de la siguiente muestra.

Para obtener un modelo matemático de la combinación de un muestreador real y de un circuito de retención de orden cero, comienza a partir del hecho de que la integral de una función impulso es una constante, se puede suponer que el retenedor de orden cero es un integrador, y la entrada al circuito de retención de orden cero es un tren de impulsos. Así que, para el modelo matemático de un muestreador real y un retenedor de orden cero se puede construir de la siguiente manera.

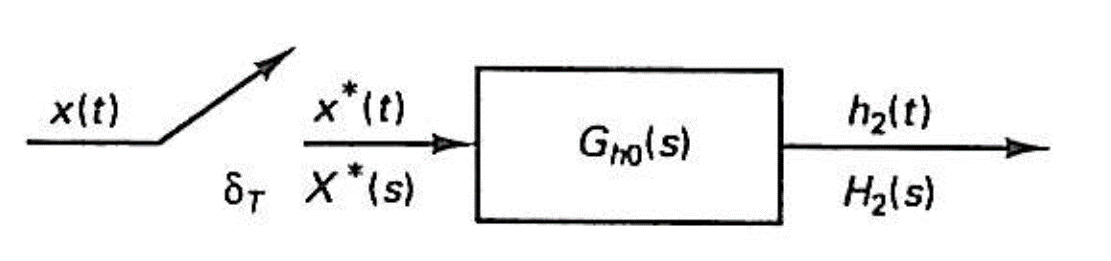

El modelo de la figura 3, se observa que representa la función de transferencia del retenedor de orden cero y

es la señal muestreada mediante impulsos de

.

En base a la figura 2, se va a suponer que la señal es cero para

. Entonces, la salida

está relacionada con

como sigue:

Si , entonces,

tiene la siguiente expresión aplicando transformada de Laplace en ambos miembros

Y en base al modelo matemático en la figura 3, la salida de este modelo debe ser la misma que la del retenedor de orden cero real. luego

Entonces

Además, si las siguientes equivalencias

y

se sustituyen en la ecuación , se tiene la siguiente expresión

Buen día!

¿Cuál es la bibliografía de referencia para este tema?

Gracias

Me gustaMe gusta

Hola Jet Black. En Referencias puedes encontrar la información obtenida…

Me gustaMe gusta